Unit - 3

**Transistor Biasing Techniques**

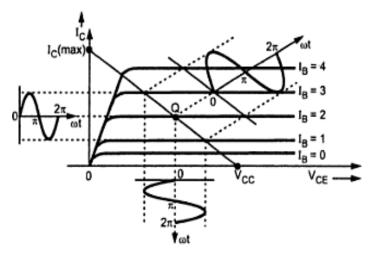

## LOAD LINE ANALYSIS

#### • DC & AC LOAD LINES:

# **Different Regions Of Operation**

| Region of Operation | Emitter Base Junction | Collector Base Junction |  |

|---------------------|-----------------------|-------------------------|--|

| Cut off             | Reverse biased        | Reverse biased          |  |

| Active              | Forward biased        | Reverse biased          |  |

| Saturation          | Forward biased        | Forward biased          |  |

## **Condition for Active & Saturation Regions**

| Transistor | V <sub>CE (sat)</sub> | V <sub>BE (sat)</sub> | V <sub>BE (active)</sub> | V <sub>BE (cut-in)</sub> | VBE (cut -off) |

|------------|-----------------------|-----------------------|--------------------------|--------------------------|----------------|

| Si         | 0.2 V                 | 0.8 V                 | 0.7 V                    | 0.5 V                    | 0 V            |

| Ge         | 0.1 V                 | 0.3 V                 | 0.2 V                    | 0.1 V                    | - 0.1 V        |

For saturation:

$$I_{\rm B} > \frac{I_{\rm C}}{\beta_{\rm dc}}$$

For active region:

$$V_{CE} > V_{CE \, (sat)}$$

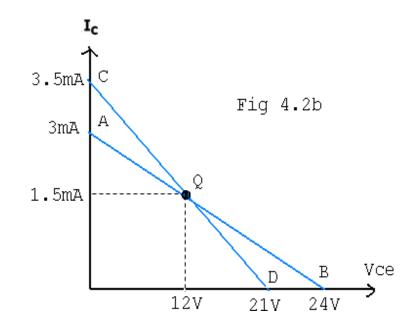

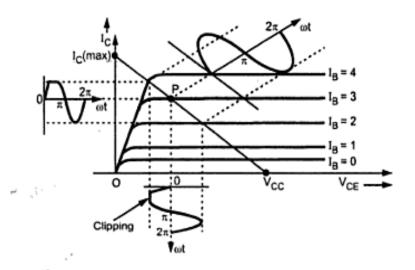

Operating point near saturation region gives clipping at the positive peaks

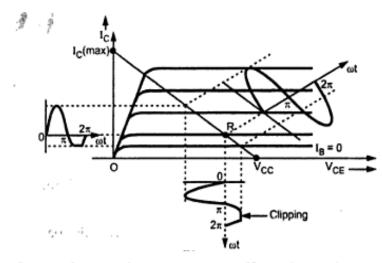

Operating point near cut-off region gives clipping at the negative peaks

Operating point at the centre of active region is most suitable

## **Transistor Biasing**

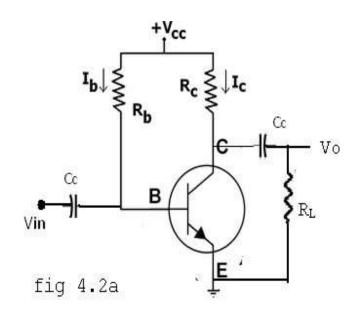

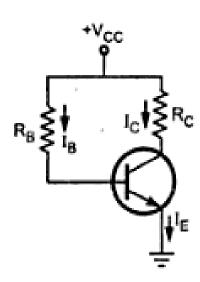

Fixed bias circuit

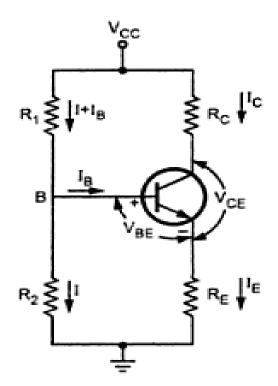

Voltage divider bias circuit